| Feature | Master 1 | Master 2 |

|---|---|---|

| Support for QNX 8.0 | — | in development |

| IP cores extension with support of RGMII and MDIO interfaces | — | in development |

| Support forXenomai 3.2 | 1.8.1405 | — |

| Support for RTX64 4.5 | 1.8.802 | 2.6.3502 |

| Support for QNX 7.1 | 1.6.55118 | 2.5.27405 |

| Support for Zynq Xenomai | 1.6.33918 | 2.5.24642 |

| Support for RTX64 4.4 | 1.6.56308 | 2.5.22913 |

| Support for INtime 7 | — | 2.5.22913 |

| MIP Framework extension | — | 2.4.56905 |

| Support for RTX64 4.3 | 1.6.55704 | 2.4.56905 |

| Timed send emulation with RTX64 NAL | — | 2.4.56013 |

| Reference design for Xilinx ZCU104 Support for Xilinx Vivado 2021.1 |

— | 2.4.55606 |

| KPA Sentinel dongle for Linux-based OS | 1.6.55503 | 2.4.55504 |

| Support for RTX64 4.2 | 1.6.55305 | 2.4.54209 |

| Support for RTX64 NAL | — | 2.4.54209 |

| FSOE for Autoconfigurator Autoconfigurator samples improvement Post validation for Autoconfigurator export |

— | 2.4.51918 |

| Restriction of background frames size | 1.6.55118 | — |

| Support for VxWorks SDK 6.9.4.12 | 1.6.54901 | — |

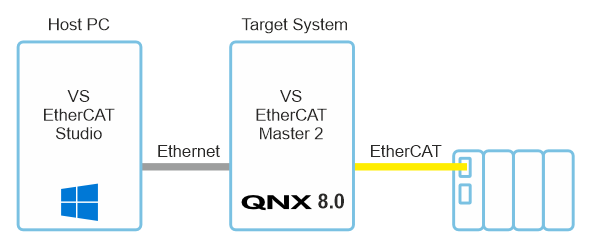

Support for QNX 8.0

Ready to take your embedded systems to the next level? Introducing full VS EtherCAT Master 2 support for the new QNX 8.0 operating system, bringing next-generation microkernel architecture to your trusted development platform.

IP cores extension with support of RGMII and MDIO interfaces

We are excited to announce the release of VS EhterCAT Master 2 for FreeRTOS with our latest Cable Redundancy and Send Scheduler IP cores, now supporting RGMII (Reduced Gigabit Media-Independent Interface) and MDIO (Management Data Input/Output) interfaces. This enhancement is designed to provide robust and efficient solutions for your networking applications.

- The integration of RGMII allows for high-speed data transfer between the FPGA and Ethernet PHY, utilizing a dual data rate mechanism that enhances performance while reducing the number of required signals.

- The MDIO interface facilitates communication between the MAC and multiple PHY devices, enabling efficient management and configuration of Ethernet devices.

These new IP cores are designed to meet the demands of modern networking applications, providing flexibility and scalability for developers. They are now available for integration into your projects, allowing you to leverage the latest advancements in Ethernet technology.

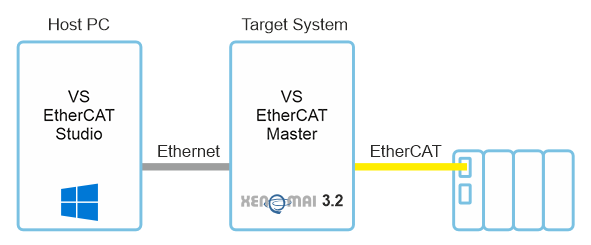

Support for Xenomai 3.2

This update provides full integration with the latest version of Xenomai 3.2, extending real-time capabilities to embedded systems and providing improved performance and stability.

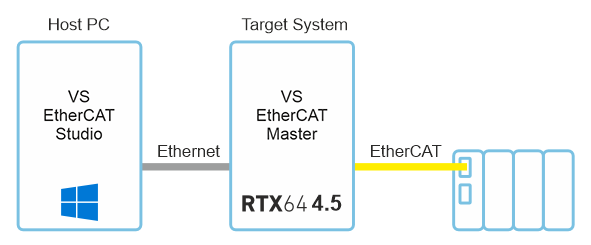

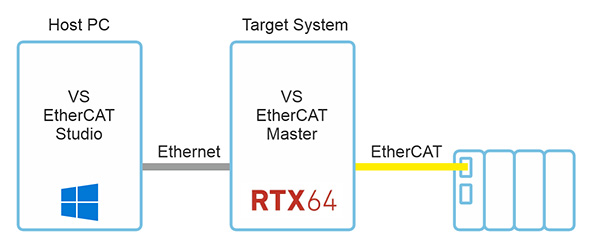

Support for RTX64 4.5

With the introduction of VS EtherCAT Master with RTX64 4.5 support, you can harness the power of advanced technology designed specifically for demanding real-time environments. Whether you are tackling complex simulation, high-speed data processing or any other real-time task, RTX64 4.5 will provide you with the tools you need.

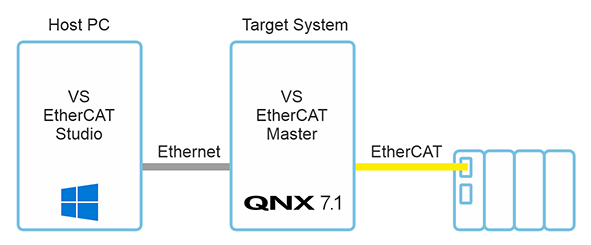

Support for QNX 7.1

With this enhancement, we have further strengthened the capabilities of our VS EtherCAT Master 2, ensuring seamless integration and exceptional performance on the

Support for Zynq Xenomai

With this new support, users can now take advantage of the features and benefits of VS EtherCAT Master 2 while running their applications on the Zynq Xenomai platform. This opens up new possibilities for automation and control systems development. Hardware Integration Package for Xilinx ZC702 Evaluation Board is also available. This powerful package takes your projects to new heights.Support for RTX64 4.4

From now on Master supports RTX64 4.4 - the latest version of RTX64.Support for INtime 7

From now on Master supports INtime 7 - the latest version of INtime.MIP Framework extension

A possibility to create executors in different threads automatically has been added into MIP Framework as the Threads Processor template.Support for RTX64 4.3

From now on Master supports RTX64 4.3 – the latest version of RTX64.

Timed send emulation with RTX64 NAL

Added Timed send emulation support for RTX64 NAL driver. With the emulation of timed sending enabled, the Master prepares the frames before the cycle starts and passes them to a separate thread (instead of the HW module in case of Hardware timed send). It sends the frames as soon as the cycle begins.Reference design for Xilinx ZCU104

New reference design for Xilinx ZCU104 Evaluation Kit has been released.Support for Xilinx Vivado 2021.1

From now on Master supports version 2021.1 of Xilinx Vivado.KPA Sentinel dongle for Linux-based OS

From now on Master licensing can be bound to Sentinel dongle on Linux-based OS (Linux Rt-Preempt).Support for RTX64 4.2

From now on Master supports RTX64 4.2 - the latest version of RTX64.Support for RTX64 NAL

From now on Master supports RTX64 Network Abstraction Layer (NAL).

Unlike the TCP/IP stack interface, the NAL makes modern Ethernet adapter features available for engineers. The NAL offers a stable, reliable deterministic network interface, which is very important at building and connecting machines.

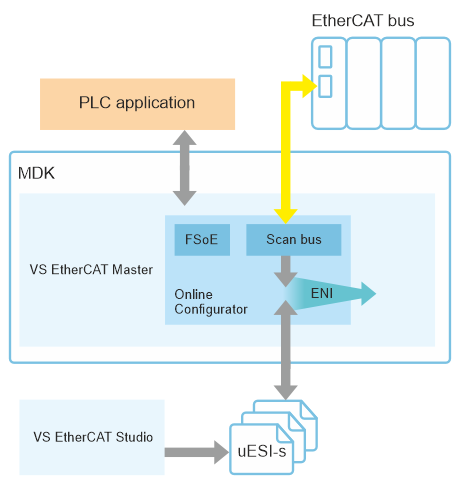

FSoE for Autoconfigurator

Parsing of safety connections and their verification have been added to Autoconfigurator.

If configured connections are not detected, Autoconfigurator generates ECAT_AC_EVENT_UNLINKED_SAFETY_CONNECTION and returns ECAT_E_AC_SAFETY_CONNECTIONS on export call.

To configure Autoconfigurator with FSoE, create the configuration in VS EtherCAT Studio, set S2S connections between safety PDOs/PDO Entries and save it to uESI and then apply it to Autoconfigurator.

Autoconfigurator samples improvement

A new Autoconfigurator export template has been added to the samples. All Autoconfigurator samples now use this template to configure VS EtherCAT Master.Post validation for Autoconfigurator export

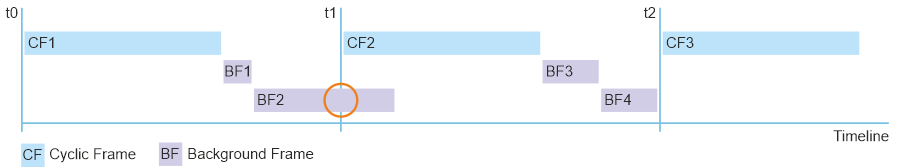

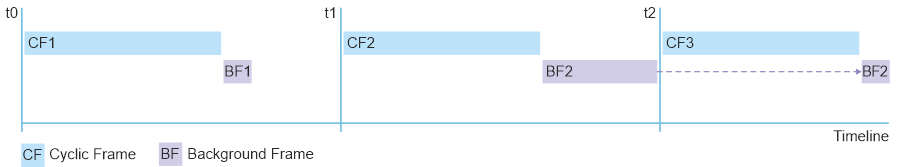

Post validation has been added to Autoconfigurator export. This allows different modules to check configuration consistency before export.Restriction of background frames size

A possibility to limit a maximal size of background frames has been added.

Background frames are all non cyclic frames. In some cases when bus load is near 100%, sending background frames can exceed the Cycle time.

Using the background frames size restriction allows to guarantee sending frames during one cycle time and to check the bus configuration.

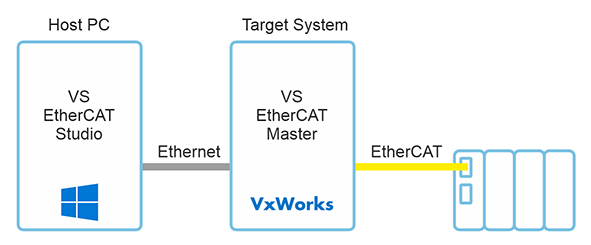

Support for VxWorks SDK 6.9.4.12

Implementation of support for VxWorks SDK 6.9.4.12.